# Hardware-Accelerated Super-Resolution

A Major Qualifying Project (MQP) Report Submitted to the Faculty of WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the Degree of Bachelor of Science in

Electrical and Computer Engineering, Computer Science

By: Will Buchta, Diyar Aljabbari, Parker Langa, Parker Lavering, Adam Spencer

Project Advisor: Professor Patrick Schaumont, PhD.

Date: May 2025

This report represents work of WPI undergraduate students submitted to the faculty as evidence of a degree requirement. WPI routinely publishes these reports on its website without editorial or peer review. For more information about the projects program at WPI, see http://www.wpi.edu/Academics/Projects.

# Abstract

This project brings machine learning and hardware development together to implement real-time video upscaling algorithms on FPGAs. Video frames from a Nintendo Wii are analyzed for variance and routed to either bilinear interpolation or a convolutional neural network for upscaling. Hardware was developed and verified in Vitis HLS C++. The two development boards used for testing and implementing the design were the KV260 and ZCU102. This report outlines the team's successes and identifies areas for improvement in future designs.

# **Executive Summary**

#### Introduction

Despite the rapid advancement of display technology and the release of monitors with higher resolutions almost every year, old media, such as retro video games, remain at the low resolution at which they were created. These games were designed for low-resolution displays available at the time of their creation and do not scale well to new screens on the market. One way to accommodate newer displays is to upscale the video with super-resolution algorithms, creating a new image that is larger and higher quality than the original. The capabilities of software alone are insufficient to achieve this goal in real-time, and hardware lacks the ease of use and flexibility that software offers. This project addresses the challenge of upscaling low-resolution video in real-time by developing a hardware/software coprocessor pipeline for FPGAs that consists of variance measurement, color space conversion, CNN upscaling, and bilinear interpolation.

The goals of this project are as follows.

- 1. Achieve real-time 2x video upscaling on the output of the Nintendo Wii, targeting 25 FPS and a resolution of  $1440 \times 1152$  at the output

- 2. Train a super-resolution model to upscale native Wii data by a factor of two

- 3. Implement a hybrid upscaling system, utilizing FSRCNN [1] and bilinear interpolation based on the variance of image tiles

- 4. Design and verify hardware IP using Vitis HLS

- 5. Optimize the hardware implementation to fit the resource constraints of the ZCU102 development board

This work was completed over the course of one academic year, during which the team designed, implemented, verified, and optimized a super-resolution pipeline on an FPGA. This project was student-led with the help of Professor Patrick Schaumont.

# Design and Methodology

Since FPGAs have limited on-chip resources, the main idea is to split an image into subsections, or "tiles," and process them based on their level of detail. If a tile has a high variance, it contains many different colors and a lot of detail, and should be upscaled via a slower, high-quality algorithm. If a tile has little variation, for example, an image of a blue sky, it should be upscaled as quickly as possible using a lower-quality but faster method. This division enables the high-quality method to be computationally expensive while avoiding wasting clock cycles on unnecessary tiles. These two methods are FSRCNN [1], a convolutional neural network designed for super-resolution, and bilinear interpolation, a simpler image upscaling technique. This paper details the design process and implementation of three main IP blocks: one designed to measure tile variance and convert color space, another to run FSRCNN, and a third to perform bilinear interpolation.

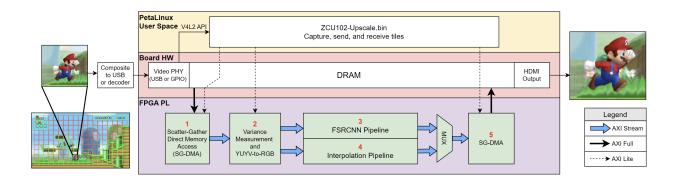

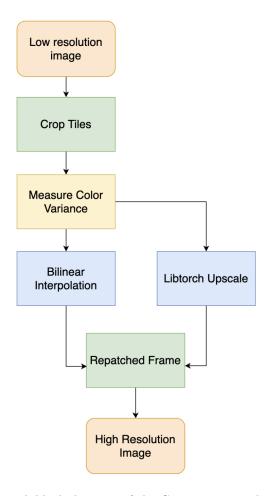

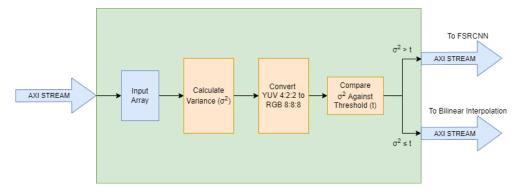

Figure 1: A system-level diagram of the upscaling process.

Additionally, it outlines the build infrastructure, software, and machine learning development surrounding these components. Figure 1 details the high-level data flow of this project.

#### Results

The team currently has a demonstration able to run bilinear interpolation on real Wii frames at 9.7 FPS with the KV260 development board. The physical interface for video input on the ZCU102 is still under development, so that demo currently only upscales a single image from a file. As for the convolution IP, it uses more resources than what is available on the KV260, so it will only synthesize for the ZCU102. The IP is functionally verified in both Python and Vitis HLS; however, the team is currently debugging issues that arise when running cosimulation and testing on hardware.

A significant bottleneck in our system was not fully identified until late in the project: transferring data to and from the programmable logic. This is because the DMA engine needs to fetch buffer descriptors every four stream beats. The latency to send a single 32 x 32 pixel tile into the FPGA is roughly 1,700 clock cycles, or approximately 17 µs at 100 MHz. Receiving a tile takes approximately 3,600 clock cycles, or 36 µs at 100 MHz. With 368 tiles, the total latency because of data transfer is 19,500 µs, or nearly 20 ms. At 25 FPS, this is half of the total budget to achieve real-time processing. Additionally, it takes 54 clock cycles to transfer one row of a tile, with only four of those clock cycles being used to actually send the data. This means that 93% of the transfer time is spent fetching buffer descriptors from DRAM.

#### Conclusions and Recommendations

The outcome of the team's work on this project proves that real-time video upscaling on an FPGA is attainable. While only one of the upscaling methods was successfully implemented on hardware, the entire design is fully verified in software. Moving forward with the project, optimizations regarding efficiency, both in terms of speed and resource utilization, as well as the quality of results, should be applied to both upscaling algorithms. This project was successful in bringing multiple areas of computer science and computer engineering together to create an embedded system.

# Acknowledgments

The team would like to thank the following for help throughout the project.

Professor Patrick Schaumont for guidance

John Eismeier for helping with IT infrastructure

Brian Jackson for providing suggestions for model development

The AMD University Partnership Program for donating a ZCU102 evaluation board

# Statement of Authorship

| Section    | Subsection                                          | $\mathbf{Author}(\mathbf{s})$    |

|------------|-----------------------------------------------------|----------------------------------|

|            | Image Upscaling                                     | Langa                            |

|            | Video Signal Properties                             | Spencer                          |

| Literature | Variance                                            | Spencer                          |

| Review     | Convolutional Neural Network                        | Langa                            |

|            | Hardware Implementation of Upscaling Techniques     | Langa                            |

|            | Verification and Universal Verification Methodology | Aljabbari                        |

|            | Functional Architecture                             | Buchta, Lavering                 |

|            | Generating Weights                                  | Lavering                         |

|            | Managing Dataflow in Hardware                       | Buchta                           |

|            | HLS: Variance and Color Space Conversion            | Spencer                          |

| Design     | HLS: Bilinear Interpolation                         | Langa                            |

| Design     | HLS: FSRCNN                                         | Buchta                           |

|            | Software Development                                | Buchta                           |

|            | Project Infrastructure                              | Buchta                           |

|            | HLS Verification Methods                            | Aljabbari                        |

|            | Software Development                                | Buchta                           |

|            | System Overview                                     | Buchta                           |

| Results    | Verification Results                                | Aljabbari                        |

|            | Example Upscaled Image                              | Lavering, Buchta                 |

|            | Introduction                                        | Langa, Spencer                   |

| Other      | Discussion                                          | Spencer, Lavering                |

| Other      | Future Work                                         | Buchta, Spencer, Lavering, Langa |

|            | Conclusion                                          | Langa                            |

# Contents

| 1 | Intr | roducti | ion        |                                                         | 1  |

|---|------|---------|------------|---------------------------------------------------------|----|

| 2 | Lite | erature | Review     | v                                                       | 3  |

|   | 2.1  | Image   | Upscalin   | ng                                                      | 3  |

|   | 2.2  | Video   | Signal P   | roperties                                               | 3  |

|   | 2.3  | Variar  | nce        |                                                         | 5  |

|   | 2.4  | Interp  | olation:   | Nearest Neighbor, Bilinear, Bicubic                     | 5  |

|   | 2.5  | Convo   | lutional 1 | Neural Networks                                         | 7  |

|   | 2.6  | Hardv   | vare Impl  | lementation of Upscaling Techniques                     | 9  |

|   |      | 2.6.1   | System     | Hardware                                                | 9  |

|   |      | 2.6.2   | Parallel   | Design Implementation                                   | 9  |

|   |      | 2.6.3   | High-Le    | evel Synthesis                                          | 10 |

|   | 2.7  | Verific | ation and  | d Universal Verification Methodology                    | 11 |

| 3 | Des  | sign    |            |                                                         | 12 |

|   | 3.1  | Functi  | ional Arc  | hitecture                                               | 12 |

|   | 3.2  | Model   | Training   | 5                                                       | 12 |

|   |      | 3.2.1   | Machine    | e Learning Design Plan                                  | 13 |

|   |      | 3.2.2   | Training   | g on an Emulated Dataset with Composite Video Artifacts | 14 |

|   |      | 3.2.3   | Address    | sing Domain Shift                                       | 15 |

|   |      | 3.2.4   | Current    | Implementation                                          | 15 |

|   | 3.3  | Manag   | ging Hard  | dware Dataflow                                          | 15 |

|   | 3.4  | High-l  | Level Syn  | nthesis Development                                     | 16 |

|   |      | 3.4.1   | Varianc    | e and Color Space Conversion                            | 17 |

|   |      |         | 3.4.1.1    | Functionality                                           | 17 |

|   |      |         | 3.4.1.2    | Variance Calculation Implementation                     | 18 |

|   |      |         | 3.4.1.3    | Color Space Conversion Implementation                   | 19 |

|   |      |         | 3.4.1.4    | Implementation Results                                  | 19 |

|   |      | 3.4.2   | Bilinear   | Interpolation                                           | 20 |

|   |      |         | 3.4.2.1    | Hardware Architecture                                   | 20 |

|   |      |         | 3.4.2.2    | Functional Modeling                                     | 21 |

|   |      |         | 3.4.2.3    | Implementation Results                                  | 24 |

|   |      | 3.4.3   | FSRCN      | N                                                       | 25 |

|   |      |         | 3.4.3.1    | Hardware Architecture                                   | 25 |

|   |      |         | 3.4.3.2    | Functional Modeling                                     | 25 |

|   |      |         | 3.4.3.3    | Implementation Results                                  | 28 |

|   | 3.5  | Softwa  | are Devel  | opment                                                  | 29 |

|   | 3.6  | Projec  | et Infrast | ructure                                                 | 30 |

|                  |       | 3.6.1           | Build Server Setup and Repository Setup                                                                                  | 30 |

|------------------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------|----|

|                  |       | 3.6.2           | Scripting and Cross-Platform Design                                                                                      | 30 |

| 4                | HLS   | S Verif         | fication Methods                                                                                                         | 32 |

|                  | 4.1   | Verific         | eation Methodology Overview                                                                                              | 32 |

|                  | 4.2   | Verific         | eation Testbenches                                                                                                       | 33 |

|                  |       | 4.2.1           | Color Space Conversion Testbench                                                                                         | 33 |

|                  |       | 4.2.2           | Bilinear Interpolation Testbench                                                                                         | 33 |

|                  |       | 4.2.3           | CNN Testbench                                                                                                            | 33 |

|                  | 4.3   | Mainta          | ainability                                                                                                               | 34 |

| 5                | Res   | $\mathbf{ults}$ |                                                                                                                          | 35 |

|                  | 5.1   | System          | n Overview                                                                                                               | 35 |

|                  | 5.2   | Verific         | eation Results                                                                                                           | 35 |

|                  | 5.3   | Examp           | ple Upscaled Image                                                                                                       | 37 |

| 6                | Disc  | cussion         | 1                                                                                                                        | 38 |

|                  | 6.1   | Consid          | deration of Public Health and Other Factors                                                                              | 38 |

|                  |       | 6.1.1           | Public Health                                                                                                            | 38 |

|                  |       | 6.1.2           | Public Safety                                                                                                            | 38 |

|                  |       | 6.1.3           | Public Welfare                                                                                                           | 38 |

|                  |       | 6.1.4           | Global Considerations                                                                                                    | 38 |

|                  |       | 6.1.5           | Cultural Considerations                                                                                                  | 38 |

|                  |       | 6.1.6           | Social Considerations                                                                                                    | 38 |

|                  |       | 6.1.7           | Economic Considerations                                                                                                  | 38 |

|                  | 6.2   | Recogn          | nizing Ethical and Professional Responsibilities                                                                         | 38 |

|                  |       | 6.2.1           | Consideration of the Impact of Engineering Solutions of this MQP in Global, Economic, Environmental, and Social Contexts | 39 |

|                  | 6.3   | Appro           | priate Incorporation of Engineering Standards                                                                            | 39 |

| 7                | Fut   | ure Wo          | ork                                                                                                                      | 40 |

| 8                | Con   | clusio          | $\mathbf{n}$                                                                                                             | 42 |

| Αį               | pen   | dices           |                                                                                                                          | 43 |

|                  | _     |                 | ronyms                                                                                                                   | 43 |

|                  | efere |                 |                                                                                                                          | 44 |

|                  |       |                 |                                                                                                                          |    |

| $\mathbf{L}^{i}$ | ist   | of Ta           | ables                                                                                                                    |    |

|                  | 1     | Input           | and output desired resolution and frame rate for the super-resolution system                                             | 4  |

|                  | 2     |                 | aparison between three upscaling methods based on three requirements relevant to the evel upscaling structure            | 7  |

|                  | 3     |                 | rce utilization comparison between floating-point and constant integer multiplications e ZCU102 board                    | 20 |

| 4    | the ZCU102. The process speed measurement is taken from the co-simulation waveforms in Vitis HLS                                                                                                    | 25 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5    | Vitis HLS synthesis results compared to total resources on the ZCU102                                                                                                                               | 3! |

| 6    | Simulation report for various verification testbenches                                                                                                                                              | 36 |

| List | of Figures                                                                                                                                                                                          |    |

| 1    | A system-level diagram of the upscaling process                                                                                                                                                     | i  |

| 2    | YUV and RGB color space channel visualization [2]                                                                                                                                                   | 4  |

| 3    | YUV 4:2:2 channel breakdown [3]                                                                                                                                                                     | 4  |

| 4    | An example of a high variance tile (left) and a low variance tile (right) taken from New Super Mario Bros. Wii                                                                                      | ļ  |

| 5    | A comparison of bicubic, bilinear, and nearest neighbor interpolation and a pixel art character [4]                                                                                                 | (  |

| 6    | A comparison of nearest neighbor and bilinear interpolation on an upscaled picture of a flower [5]                                                                                                  | 6  |

| 7    | An example convolutional neural network [6]                                                                                                                                                         | 7  |

| 8    | The differences between the Super-Resolution Convolutional Neural Network and the Fast Super-Resolution Convolutional Neural Network [1]                                                            | 8  |

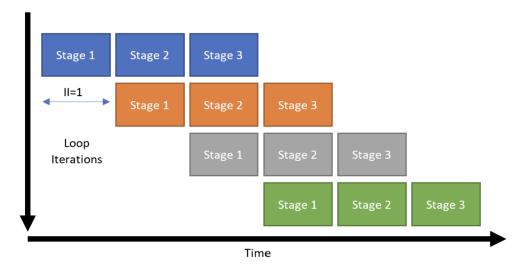

| 9    | An illustration of a procedure with three processes that have no pipelining, so that the next process only starts after the first one is completed [7]                                              | 10 |

| 10   | An illustration of a procedure with four processes that has pipelining with an initiation interval of one, so that the next process starts one clock cycle after the previous one is initiated [7]. | 10 |

| 11   | A block diagram of the C++ system architecture.<br>                                                                                                                                                 | 13 |

| 12   | A flowchart detailing the process of determining next steps when training the model                                                                                                                 | 14 |

| 13   | A flowchart illustrating the development process for IP blocks using HLS                                                                                                                            | 17 |

| 14   | A block diagram of the variance and color space conversion IP                                                                                                                                       | 18 |

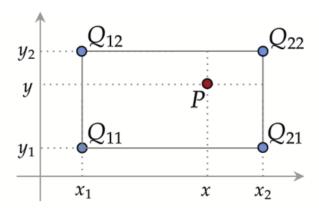

| 15   | A graphical representation illustrating the values used in Equation (8) [8]                                                                                                                         | 20 |

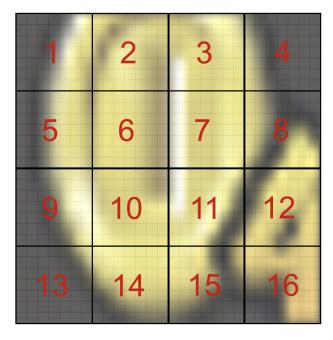

| 16   | The image from the coin tile test broken into 16 7 x 7 pixel sections as is done in the bilinear interpolation block                                                                                | 21 |

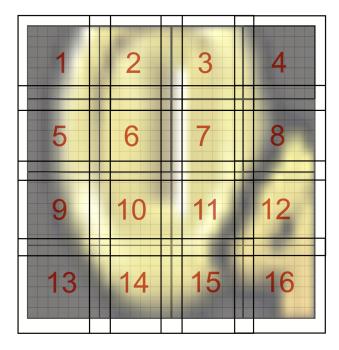

| 17   | The image from the coin tile test broken into 16 7x7 pixel chunks illustrating the chunk overlap necessary for successful interpolation                                                             | 22 |

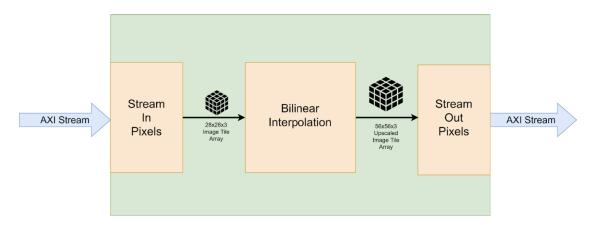

| 18   | A block diagram illustrating the structure first implementation of the bilinear interpolation IP in HLS                                                                                             | 22 |

| 19   | A code snippet showing the process of interpolating a pixel with unroll statement                                                                                                                   | 23 |

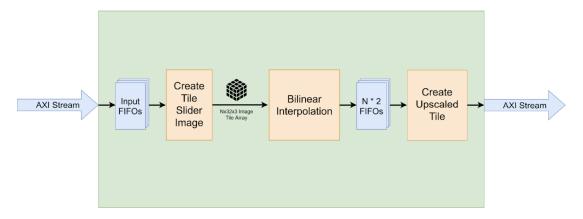

| 20   | A block diagram illustrating the structure of the final implementation of the bilinear interpolation in HLS                                                                                         | 24 |

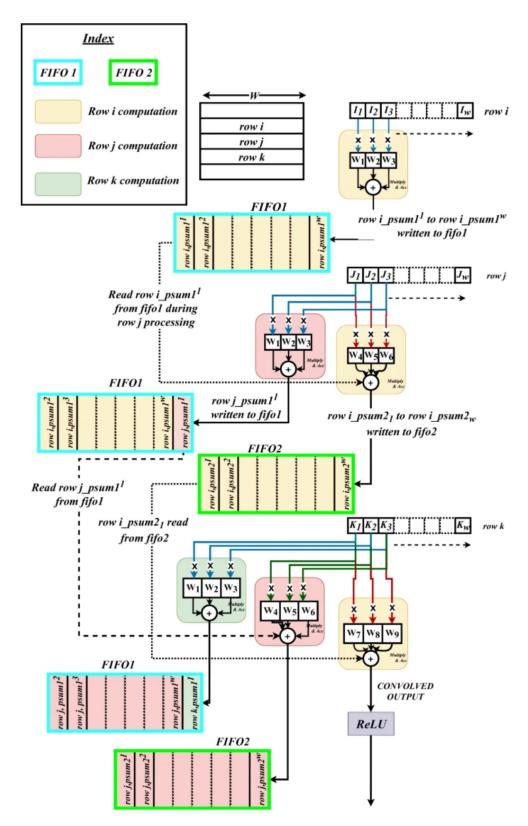

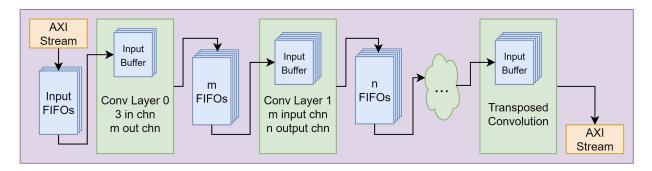

| 21   | FIFO-psum architecture of convolution operation [9]                                                                                                                                                 | 26 |

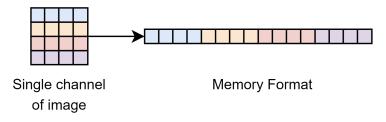

| 22   | Memory format of input and output channels                                                                                                                                                          | 27 |

| 23   | CNN architecture in Vitis HLS                                                                                                                                                                       | 27 |

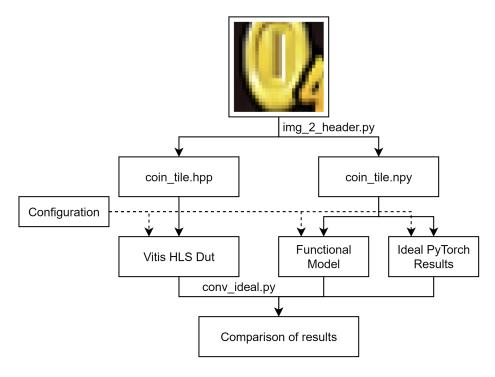

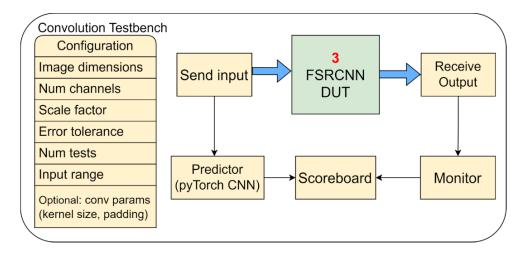

| 24   | Diagram of testing setup for convolution                                                                                                                                                            | 2  |

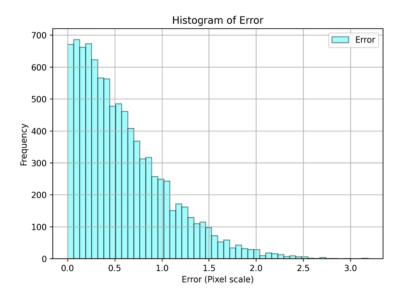

| 25 | Accumulated DUT error for FSRCNN in Vitis HLS vs. PyTorch                                                                    | 28 |

|----|------------------------------------------------------------------------------------------------------------------------------|----|

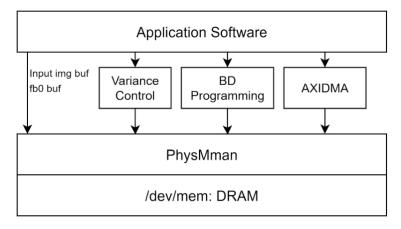

| 26 | Application software high-level overview                                                                                     | 29 |

| 27 | A diagram of the repository's structure                                                                                      | 31 |

| 28 | A block diagram showing testbench component structure                                                                        | 32 |

| 29 | A high-level block diagram of the convolution testbench                                                                      | 34 |

| 30 | The output image that was generated after a training epoch, showing the final FSRCNN model upscaling a cropped emulated tile | 37 |

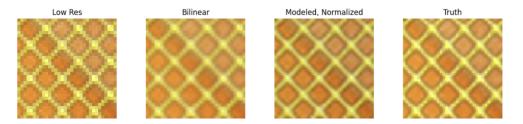

| 31 | The left image shows a raw upscaled 2x Wii frame. The right image shows a style-shifted Wii frame using CUT                  | 37 |

# 1 Introduction

Developments in computer monitors over the past 20 years have led to an increased adoption of higher-resolution displays by the general public [10]. Television production has shown a similar increase with the adoption of 4K TVs in residential households in the US increasing from 1% in 2014 to 31% in 2018 [11]. Despite this, much of the available media does not utilize the full resolution available on these displays. Graphics industry leaders, such as Nvidia, are capitalizing on this trend by developing super-resolution algorithms compatible with their GPUs, which can enhance the quality of low-resolution videos provided by streaming services through AI upscaling [12]. However, these advancements generally focus on media that is already in Full High Definition, which is 1920 x 1080 pixels. Simultaneously, there is a continued interest in retro video games such as Super Mario Bros., Minesweeper, Tetris, and Final Fantasy [13]. These factors combine to illustrate a demand in the market for creating high-level video resolution methods for low-resolution source material that function in real-time.

Retro video games present not only an upscaling challenge due to their low resolution, but also because of the distinctive art style employed. Machine learning applications of AI super-resolution have primarily focused on real-world images, as seen in previous research papers [1][14][15]. However, video game inputs differ in style and complexity. While the original art style should be maintained, the upscaling method must enhance the image's detail, rather than simply increasing the number of pixels. Additionally, latency needs to be minimized to provide a seamless and enjoyable user experience. Upscaling applications using a combination of hardware and software has been the focus of several research projects; however, these efforts have yet to specifically target video game applications [1][14][15].

The objective of this project was to replicate the work laid out in "FPGA-Based Real-Time Super-Resolution System for Ultra High Definition Videos" [15] and implement a hardware accelerator for super-resolution targeted at the New Super Mario Bros. Wii video game under the following constraints:

- 1. Ensure the architecture is fast enough to create a real-time output

- 2. Create a design whose resource utilization fits on the selected hardware

- 3. Complete the project within an eight-month time frame

The native output of the Nintendo Wii is 576i, spanning 720 pixels horizontally and 576 pixels vertically. Given the level of upscaling necessary to increase a standard-definition input of 576i by a factor of two to 1440 x 1152, software alone cannot operate with sufficient efficiency to perform the required computations within the constraints of a real-time application. The project was first implemented on a Kria KV260 Vision AI and later on a ZCU102 Zynq UltraScale+ $^{TM}$  MPSoC development board.

Figure 1 details the high-level flow that constitutes our system. Due to hardware limitations, input images are upscaled as a series of smaller 32 x 32 pixel tiles. The system has five main steps: programming a DMA engine to send an image frame down as a series of tiles, performing a variance measurement on each tile, converting it from the source (YUV) to destination format (RGB), upscaling with bilinear interpolation or the Fast Super-Resolution Convolutional Neural Network (FSRCNN), and using scatter-gather DMA to transfer the upscaled tiles back to a frame buffer in DRAM [5][7]. If an image tile has a high variance, it is sent through the computationally expensive FSRCNN pipeline; else, it is interpolated. Each major IP block was developed using Vitis High-Level Synthesis (HLS) to allow for rapid design iterations. The creation of IP blocks also required verifying their functionality, for which the team created a series of testbenches.

This report outlines the steps taken by the team to address the complex process of hardware-accelerated image upscaling. A list of acronyms (Appendix A) is provided to aid the reader in understanding various image processing terminology. Section 2 discusses the prior research necessary to understand the image processing field and the insights it yields for the team's implementation. Section 3 outlines the design process and methods for each subset of the project, specifically focusing on aspects such as machine learning, variance, color space conversion, bilinear interpolation, FSRCNN, application software development, and build infrastructure. Section 4 describes the verification methodology for each IP unit. After individual IP outcomes are described in their relevant design section, the results section details the system-wide outcomes.

The report concludes with a discussion about ethical concerns, future work, and a summary of all project work. This project was student-led with the help of Professor Patrick Schaumont.

# 2 Literature Review

The literature review for this report details the background knowledge necessary to successfully implement the project goals. It begins by providing a broad overview of image upscaling, then delves deeper to offer information about video signal processing. Next, it discusses the theoretical and mathematical background for variance calculations, interpolation upscaling schemes, and convolutional neural networks. It then details hardware design concepts such as the systems available, as well as parallelization and pipelining. The hardware implementation also provides insight into HLS and its applications in FPGA development. Finally, it discusses verification strategies for projects that involve both hardware and software components.

# 2.1 Image Upscaling

Image upscaling is the process of taking images or videos and increasing their resolution to increase size and/or improve quality. While this may seem straightforward, to perform this increase, new information must be added to the image by adding new pixels. The process of increasing an image beyond its original dimensions or resolution is referred to as super-resolution, and is the focus of significant research due to its complexity [16]. Additionally, the issue of upscaling images has a quadratic complexity, given that for every scale factor of two, the number of pixels increases by a factor of four. The core of modern super-resolution techniques lies at the intersection of hardware and software, with hardware development focusing on efficient implementation and software development focusing on leveraging machine learning to enhance the value of upscaled images beyond their original content. Both hardware and software developers require an understanding of image processing and prior work to successfully implement an upscaling algorithm.

Those approaching the problem from a hardware perspective must understand the complexities and potential bottlenecks of upscaling approaches, as well as the intensive calculations that some methods require. Additionally, identifying bottlenecks allows for the allocation of resources to overcome them and create speed-ups.

The work previously done in image processing, regardless of whether it focused on super-resolution, allows an informed approach to system design and implementation. There is currently a wide variety of applications utilizing image processing, ranging from using image filters in video games as shaders to object detection and facial recognition. Applications that utilize detection or recognition focus on manipulating or interpreting pixel values by adding external information, and although they do not increase the size of the image, they resemble convolutional neural network (CNN) methods used for image upscaling [17][18]. As such, research surrounding convolutional neural networks for image processing was completed before the development of a methodology.

# 2.2 Video Signal Properties

The two main components of a video are its **frame rate** and **resolution**. Frame rate refers to the number of images displayed per second, creating the illusion of motion; a higher frame rate results in a smoother video. Resolution indicates how many pixels span the horizontal and vertical axes of each frame, and a higher resolution means a higher perceived quality of the video being displayed. By testing and measuring the frame rate and resolution output from the Wii in software, the team found that it outputs 25 frames per second (FPS) at a resolution of 576i. These two metrics helped align the project's goals, as they quantified the required computation data rate for real-time processing, as well as the initial and final desired dimensions of the frames to be upscaled. By definition, real-time video upscaling involves manipulating video under two simple conditions: retaining the original timing and increasing the video's scale. The success of this project is largely quantified by these two parameters once all elements are implemented. Table 1 enumerates the input resolution and frame rate, as well as the desired output resolution and frame rate of the super-resolution system.

Color space describes a standardized manner of representing colors for image or video formats. Images and video are split up into pixels, which can be represented in various color spaces. Each color space

Table 1: Input and output desired resolution and frame rate for the super-resolution system.

| Device                          | Horizontal Pixel Count | Vertical Pixel Count | Frame Rate | Pixels/second |

|---------------------------------|------------------------|----------------------|------------|---------------|

| Nintendo Wii                    | 720                    | 576                  | 25         | 10,368,000    |

| Desired Super-Resolution Output | 1440                   | 1152                 | 25         | 41,472,000    |

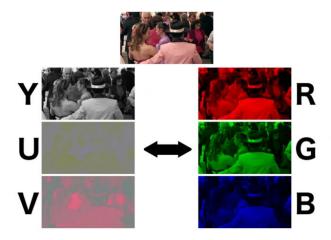

Figure 2: YUV and RGB color space channel visualization [2].

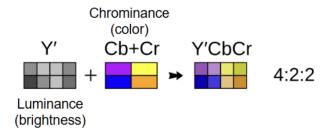

Figure 3: YUV 4:2:2 channel breakdown [3].

has a way of dividing pixel data into separate components, which combine to create a color that can be rendered on a screen. An image can have hundreds of thousands or even millions of pixels, each capable of representing millions of different colors.

Two of the most common color spaces used in video applications are YUV and RGB. YUV consists of three channels: luminance, chrominance-blue, and chrominance-red. The Y channel, or luminance, of a YUV pixel represents its brightness level, resulting in a grayscale mapping of the image when displayed independently. The U and V channels express the amount of blue and red that belongs in each pixel, respectively. RGB uses three channels as well, being the amount of red, green, and blue in each pixel. In any color space, each of these channels is primarily represented by an 8-bit number, meaning that the values range from 0 to 255. Figure 2 illustrates the difference between the YUV and RGB color spaces, showing what each channel looks like when displayed individually.

Both of these color spaces have many different variations, using different bit widths per channel, or shared channels between pixels, but the variations that are utilized in this design are YUV 4:2:2, RGB 8:8:8, and RGB 5:6:5. As seen in Figure 3, the 4:2:2 variation of YUV uses chrominance sampling on every other pixel, reducing the amount of memory each pixel takes up, while subsequently reducing quality [19]. YUV 4:2:2 requires 32 bits of memory for every two pixels, making it more memory-efficient compared to the RGB 8:8:8 standard. The only difference between RGB 8:8:8 and RGB 5:6:5 is the number of bits used per channel; RGB 8:8:8 uses 8 bits per channel, while RGB 5:6:5 uses 5 bits for red, 6 bits for green, and 5 bits for blue, making each pixel use a total of 16 bits instead of 24.

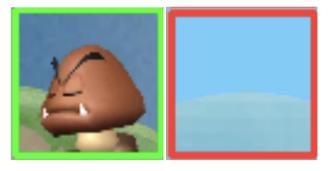

Figure 4: An example of a high variance tile (left) and a low variance tile (right) taken from New Super Mario Bros. Wii.

### 2.3 Variance

Variance is a common statistical calculation that indicates the amount of dispersion between data points in a set [20]. Measuring variance in a dataset has numerous applications in statistics and probability, as well as in finance, investment, and machine learning. In these fields, variance is used to estimate the likelihood of an expected outcome. It can quantify the stability or volatility of a dataset and imply the existence of outliers.

The two primary types of variance are sample variance and population variance. Sample variance, as implied by its name, estimates the overall variation using a subset of the entire dataset. Population variance considers every data point in the set, providing an exact value for the amount of dispersion in the dataset. Variance, by definition, is the average of the squared differences of each data point from the mean.

A high variance indicates a large spread between data points and their mean. In the context of image processing, high variance indicates a high variety of colors in the image, while low variance means the image contains mostly similar colors. Figure 4 shows images taken from *New Super Mario Bros Wii*, where the tile outlined in green has a high variance, 934.91, and the one outlined in red has a much lower variance of 16.26. The variance of these two images was calculated on the RGB color space using the NumPy Python library.

### 2.4 Interpolation: Nearest Neighbor, Bilinear, Bicubic

There are two types of image upscaling: those that use solely the information contained in the image or video, and those that introduce outside data, generally from trained machine learning models. Methods that only use data contained within the image are generally more cost-effective in terms of resource utilization, as they require fewer and less intensive calculations, and there is no need to store additional data. One of these methods, interpolation, has three common variations: nearest neighbor, bilinear, and bicubic [21]. While these methods compute the upscaled image differently, all require the algorithm to be run on each channel of an image. Most images are stored in RGB format, meaning that the algorithm must be applied to the red, green, and blue channels of the image and then be recombined to create a single three-dimensional array of pixel values for the upscaled image.

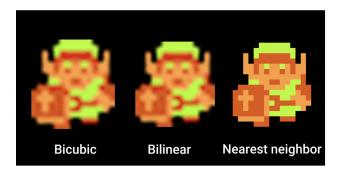

Nearest neighbor is the simplest, both in terms of computational complexity and resource utilization. It involves iterating through the pixels of the upscaled image, identifying the pixel in the original image that is closest to the interpolated pixel, and copying the value of that pixel [22]. Outside of calculating which pixel in the original image is closest to the upscaled pixel, which is necessary for all forms of interpolation, the only action that is performed by hardware is the duplication of a value. While this algorithm is the most efficient, the results are fairly poor. As the level of upscaling increases, the resulting image becomes more pixelated. This approach may be suitable for some pixel art applications that require the exact shape and pixel distribution of the input (Figure 5), but it is not well-suited for applications that seek smooth and clear imagery (Figure 6).

Figure 5: A comparison of bicubic, bilinear, and nearest neighbor interpolation and a pixel art character [4].

Figure 6: A comparison of nearest neighbor and bilinear interpolation on an upscaled picture of a flower [5].

**Bilinear interpolation** is an alternative to nearest neighbor [22]. Similar to the nearest neighbor method, it identifies the pixels in the original image that are closest to the upscaled pixel being calculated. However, instead of copying the nearest value, it performs a weighted average.

**Bicubic interpolation** is the third method, which employs a similar approach to weighting pixel values based on distance and summing the results, but with more data points [23]. Using bilinear or bicubic interpolation results in less pixelated images, as their calculations involve a series of averages; however, this approach leads to results that appear blurry (Figures 5 and 6) [22].

Unlike nearest neighbor, bilinear and bicubic calculations require more hardware resources. Although interpolation involves some division operations, the majority are addition, subtraction, and multiplication, which are fast on hardware due to the ability to parallelize elements of the calculation process. Additionally, given that pixel values in the RGB color space are 8-bit, it avoids computationally complex multiplications of large numbers. The difference in hardware resource usage depends on the number of input pixels accessed for each output pixel calculation. Bicubic interpolation requires four times the number of pixels that bilinear interpolation does, which increases the number of memory accesses-a common bottleneck in image processing. As such, when implementing these algorithms, special attention must be paid to how the input pixel values are stored.

All interpolation methods that use solely the information contained in the original image are subject to the introduction of artifacts, which must be handled with caution [24]. While some artifacts, such as those caused by overflow errors, can be mitigated through techniques like normalization, others, like pixelation, must be addressed by selecting a different algorithm.

To determine which algorithm best fits our goals and constraints, we created a table (Table 2) outlining the benefits and drawbacks of each method. By outlining the system's requirements and assigning a priority value to each requirement, the team determined that bilinear interpolation best met our needs. The highest priority requirement was achieving a result that wasn't pixelated, for it to blend with the convolutional neural network. Of the three methods, nearest neighbor was the only one that failed this criterion, and as such, we decided against it. The other two requirements were calculations and memory

Table 2: A comparison between three upscaling methods based on three requirements relevant to the high-level upscaling structure.

| Interpolation Type     | Number of calculations per pixel (low priority) | Number of memory accesses per pixel (medium priority) | Non-pixelated result? (high priority) |

|------------------------|-------------------------------------------------|-------------------------------------------------------|---------------------------------------|

| Nearest Neighbor       | 0                                               | 1                                                     | No                                    |

| Bilinear Interpolation | 19                                              | 4                                                     | Yes                                   |

| Bicubic Interpolation  | 51                                              | 16                                                    | Yes                                   |

Figure 7: An example convolutional neural network [6].

accesses, with memory access ranked higher than calculations because there were more resources available for calculations than were available for memory storage. Additionally, memory usage posed a greater threat to speeding up calculations, as it limited the effectiveness of pipelining. However, regardless of the priority of the number of calculations and memory accesses required, bilinear interpolation uses fewer resources than bicubic interpolation.

# 2.5 Convolutional Neural Networks

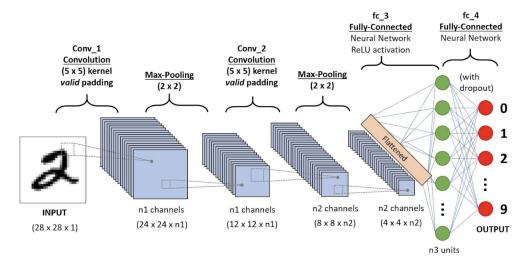

The other set of methods surrounding image upscaling involves introducing external data. One of these methods, convolutional neural networks (CNNs), rely on performing convolutions on the input image using a series of pre-trained kernel weights. CNNs are broken into three main sections called layers: input, hidden, and output layers [25]. Input layers connect directly with the input data, hidden layers contain data calculation and manipulation, and output layers produce the results of the CNN. Regardless of the layer type, the output of each convolution layer is called a feature map.

When CNNs are used for image processing, only the input and output layers have the same format as the color space being used - the dimensions of hidden layers are often varied. The number of hidden layers varies depending on the structure of the CNN, and the function of each layer depends on the number of weights used and what traits the weights are trained to emphasize. Due to the detail contained in images, the number of weights used per hidden layer and the depth of the resulting feature map are generally larger than the number of color channels in the original image. While this allows for more detail in the upscaled image, it is one element of CNNs that requires more resources than the previously mentioned methods of upscaling. Figure 7 shows a typical architecture of a convolutional neural network.

Each layer of a CNN consists of multiply and accumulate steps, which combine input image pixel values with pre-trained kernel weights [26]. While there are multiple ways to convolve two 2D matrices, many image processing applications use matrix multiplication techniques or transposed convolutions. Convolving

Figure 8: The differences between the Super-Resolution Convolutional Neural Network and the Fast Super-Resolution Convolutional Neural Network [1].

large quantities of data can utilize transformations into other domains, such as the signal domain, reducing the complexity of calculations. However, for CNN pipelines with a few layers or ones that take in relatively small-dimensional images, the process of converting domains can prove more computationally intensive than the resources saved by the conversion. Papers that detail real-time convolutional neural networks often discuss using vector-matrix multiplications [1][15][27]. Multiplications of small numbers are efficient on hardware, so matrix values and kernel weights can be implemented on an FPGA without a significant drain on resources.

Many neural networks use convolutional layers and fully connected layers [27]; convolutional layers combine feature maps with kernel weights through 2D convolutions, while fully connected layers map the results of convolution layers to a known dataset. This is often used to identify the features distinguished in the convolutional layers [28].

Fully connected layers are essential to CNNs, whose primary aim is image identification or facial recognition. Given that the goal of image upscaling is not to produce a description of what is being upscaled, but instead to increase the resolution of those features, many super-resolution CNNs are constructed mostly or entirely of convolutional layers. These layers identify important elements of the image that must be retained as resolution is increased, and they utilize the further application of trained weights to ensure the resulting quality matches that of images known to possess those qualities.

In addition to these layers, Rectified Linear Units (ReLUs) are applied as activation functions after a convolution to introduce non-linearity. ReLUs are necessary because they enable multiple layers to be used in a CNN, thereby creating a network [29]. They are necessary to introduce non-linearity to the network, given that convolution layers of matrix multiplications are solely linear operations. For a network to identify complex features, as required by a system that identifies a variety of features within different image frames, the network must include some level of separation between each convolutional layer. This separation ensures that each layer uses its convolution with feature weights to identify different elements within the image. Although there are many types of ReLUs, recent research notes the effectiveness of Parametric ReLUs (PReLUs) for super-resolution CNNs [15]. The purpose of a PReLU is still as an activation function, but their ability to learn makes them quicker to train with fewer resources [30].

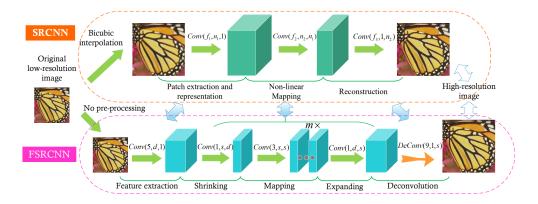

Two well-known implementations of a CNN for super-resolution have been developed to increase an image's dimensions [1][14]. The first, Image Super-Resolution Using Deep Convolutional Networks, describes upscaling the input image using bicubic interpolation before the CNN is applied [14]. This method leverages the efficiency of interpolation to perform the change in dimensions and applies the increased resolution to the interpolated result, thereby helping to recover details lost when using interpolation alone. One downside of this method is that increasing the image dimensions at the start of the CNN means that all convolutional layers perform calculations on the larger image, resulting in more hardware being used for calculations and value storage. Another implementation, Accelerating the Super-Resolution Convolutional Neural Network,

addresses this downside by moving the step that increases the image's dimension to the end of the CNN with a deconvolution layer [1].

These two implementations also differ in the types of convolutional layers they use. SRCNN consists of only three convolutional layers: patch extraction and representation, non-linear mapping, and reconstruction. The second implementation, FSRCNN, has more resources to dedicate to the convolutional layers, given that each layer is smaller, allowing for more convolutional layers in total. As such, this implementation has layers for feature extraction, shrinking, multiple mapping steps, and expanding. The graphical representation of these methods is illustrated in Figure 8 [1].

# 2.6 Hardware Implementation of Upscaling Techniques

# 2.6.1 System Hardware

When implementing image upscaling on hardware, resource management and utilization are crucial considerations. Interpolation algorithms can have relatively small hardware footprints due to their minimal computational requirements. While there are some limitations when it comes to memory access, due to multiple calculations requiring the same pixel values from the original image, many of these limitations can be navigated by dictating memory access of certain calculations or storing multiple copies of an input image. However, hardware challenges rapidly increase when implementing a CNN. Not only do CNNs require many more calculations than interpolations do, but they also have higher memory usage due to the number of feature maps and weights that must be stored for each convolution layer. Complex CNNs can have millions of parameters and use billions of operations per input image [26]. Simpler CNNs, such as those detailed in [1] and [14], use significantly fewer resources, but still require careful resource allocation when implemented on hardware.

Many hardware implementations of image processors are carried out on FPGAs, given their versatility, rapid development time, and potential for high performance. However, FPGAs have limited resources for operations and memory storage [31], making the implementation process of a super-resolution CNN require careful consideration of resource allocation when determining the amount of calculations and the level of detail within each calculation. For CNNs that use weights that must be stored in external memory, high-precision values such as 32-bit floating-point numbers can cause bandwidth issues when loading weights into memory for calculations. In addition to the memory consumption, these high-precision numbers use more logic resources than their fixed-point counterparts.

Existing studies highlight how efficient use of FPGA resources can improve the quality or speed of an algorithm by up to 90% [31]. This resource utilization refers not only to bandwidth optimization for different data types but also to buffer management and simplifying logic. Implementers of CNNs should minimize external data access for values such as weights or feature maps by carefully handling data reuse. If done incorrectly, this can require reconfiguring the FPGA for different computation layers, which allows the reuse of some calculation resources, but drastically increases the time taken for upscaling. For super-resolution CNNs to achieve real-time implementation, this must be avoided.

#### 2.6.2 Parallel Design Implementation

Research focusing on speed-ups within CNNs highlights the importance of parallel computation within and across convolution layers [26][31]. Parallel computation across layers focuses on performing multiple convolutions simultaneously, while parallelization within layers focuses on efficient loop unrolling and pipelining. Additionally, creating scalable CNN modules that allow the level of parallel computation to be quickly adjusted by changing a few high-level parameters enables tailoring resource usage to fit within different hardware constraints [26]. This is essential when working with different algorithms or across multiple FPGAs with different distributions of logic resources. Additionally, some research suggests implementing uniform loop unrolling factors across different convolutional layers [31]. This standardization ensures system-wide consistency, which is necessary when managing data flow in real-time.

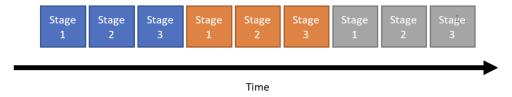

Figure 9: An illustration of a procedure with three processes that have no pipelining, so that the next process only starts after the first one is completed [7].

Figure 10: An illustration of a procedure with four processes that has pipelining with an initiation interval of one, so that the next process starts one clock cycle after the previous one is initiated [7].

One parallel implementation, pipelining, presents complications due to the potential overlap within processes. Pragma statements force the program to start another iteration of a process every specified number of clock cycles. A visual example of this can be seen in Figures 9 and 10, which highlight a process with three stages. Figure 9 illustrates an implementation without pipelining, where one process must fully complete before the next one begins. Figure 10 shows a version with an initiation interval of one. This means that a new process is initiated every cycle, resulting in overlap between processes. While specifying a low number can lead to heavy pipelining, it can drastically increase FPGA resource usage or cause complete timing failure.

If a system cannot meet the requested pipelining requirements, timing violations can occur. Some of these errors, such as initiation interval (II) violations, will cause a system to, for example, synthesize less effectively as it allocates resources for a timing goal that is unfeasible to achieve on the available hardware.

# 2.6.3 High-Level Synthesis

To work in hardware, a programming language or structure must be selected. While the standard is to use a hardware description language (HDL) such as Verilog, there are benefits to coding in C++ within the High-Level Synthesis (HLS) framework. Using Vitis HLS, C++ code is synthesised into a register transfer level (RTL) description. Similar to how working with FPGAs provides flexibility not available with Application-Specific Integrated Circuit (ASIC) design, working with HLS yields a quicker design phase than when coding directly in HDL. HLS abstracts many complex elements of HDL coding, and while HDL provides a finer level of control, implementing complex computation, such as a CNN, using HLS speeds up development time.

HLS addresses the challenges associated with hardware-level implementation through allowing con-

trol over synthesis and design optimization using pragma statements [32][33]. These control tools include resource allocation, binding, and scheduling, as well as control over the implementation of loops and streams regarding synthesis [34][35]. Memory control allows you to link specific variables or arrays with blocks of memory, such as URAM or BRAM. This level of control is essential when working on a board with varying amounts of memory resources or when the variables being stored require a specific type of memory access. The structure of HLS also contains several options for data control, specifically in relation to parallelizing processes [35]. Two such structures are for loop unrolling and pipelining, but both come with resource trade-offs. If implemented correctly, they allow for an overall processing speedup; however, they may require high quantities of logic resources, such as LUTs or DSPs, if the desired pipelining is aggressive [35]. Finally, beyond pragmas, systems of upscaling images using multiple stages will necessitate a method for passing values between functions or IP blocks, and HLS allows automatic creation and control of AXI4 protocols for this data transfer.

# 2.7 Verification and Universal Verification Methodology

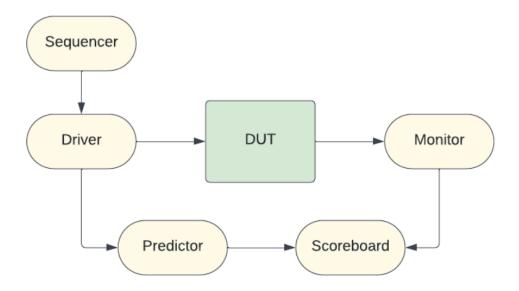

Functional verification is a crucial step before hardware implementation because it ensures that an HLS implementation behaves exactly as its specification dictates. With modern digital designs containing millions of components, exhaustive formal proofs, and testing every possible scenario is impractical. Instead, verification relies on randomized, coverage-driven simulation to expose corner-case behaviour. The Universal Verification Methodology (UVM) is the industry standard framework for this task and plays a pivotal role. UVM packages a library of SystemVerilog base classes that encourage a layered architecture: sequences produce transactions, a driver converts those transactions into pin-level activity, a monitor observes the DUT's outputs non-intrusively, and a scoreboard compares them against a reference model [36]. The infrastructure, with its agents, environments, virtual interfaces, and configuration databases, is scalable and reusable, efficiently separating stimulus generation from protocol details and reference checking.

When using Vitis HLS, the device under test (DUT) is not in SystemVerilog but in C++. HLS comes with a built-in simulator, which compiles the DUT and a C++ testbench into an executable. Although this environment lacks UVM's libraries, the same concepts can be recreated in C++ with classes and helper functions. With C++, random stimulus corresponds to a sequence object that fills standard containers, such as streaming FIFOs. The driver is a small wrapper that packs the data into AXI-Stream stream beats and asserts handshake signals, the monitor is a symmetric unpacker, and the scoreboard is a comparator that reports mismatches and collects coverage metrics. HLS enables the parameterization of types within the C++ testbenches, allowing the same driver/monitor pair to be used for 8-, 32-, or 128-bit data widths, thereby achieving the interface reusability that UVM advocates. As such, the typical verification flow in HLS mirrors a UVM test. It compiles the DUT and instantiates a highly parameterized C++ testbench that embodies sequence, driver, monitor, and scoreboard roles. The testbench runs thousands of randomized iterations in C++ simulation and finally invokes Vitis HLS cosimulation to ensure that gate-level elaboration preserves the observed functional behavior [36].

The verification process employed the Monte Carlo method [37], generating thousands of randomized test inputs to simulate a wide range of scenarios and edge cases. Each test iteration used an independently sampled stimulus, allowing the testbench to explore the input space probabilistically rather than exhaustively. This approach gives strong statistical confidence that if no errors are observed across a large number of trials, the design will likely behave correctly in real-world use; when failures would otherwise occur, it has a very low probability [37].

In short, while the language and libraries differ, the methodology of UVM, being separation of concerns, transaction-level stimulus, and self-checking tests, maps cleanly onto HLS C++ testbenches, providing HLS designers with the same disciplined verification practices that have been long-established in conventional RTL development.

# 3 Design

This section provides an overview of how the team collaborated to develop the entire system. In this context, "design" provides a comprehensive explanation of how the team developed and implemented each system, where individual contributions overlapped, and how everything came together as a cohesive whole.

### 3.1 Functional Architecture

As mentioned in Section 1, the design of this project is centered on the architecture outlined in He et al. [15]. Since FPGAs have limited on-chip resources, the main idea is to split an image into subsections, or "tiles," and process them based on the variation of information they contain, as measured by their variance. If a tile has a high variance, it contains a lot of visual variation and should be upscaled via a high-quality algorithm. If a tile has low variance, for example, an image of a blue sky, it should be upscaled using a lower-quality but faster method. This split enables the high-quality method to be relatively computationally expensive while avoiding wasting clock cycles on unnecessary tiles. These two methods are FSRCNN, a convolutional neural network designed for super-resolution, and bilinear interpolation, a simpler image upscaling technique. This process is referred to as the "tile pipeline".

Our team developed a comprehensive high-level functional model that contained the entire system workflow. This functional model serves two purposes: validating the system and confirming the pipeline for hardware implementation, as well as verifying that the entire system functions correctly. The functional model outlined the complete pipeline, including cropping tiles, variance calculation, upscaling, repatching, and outputting to the video device. Additionally, the team used it to confirm that no tiles needed to overlap in the final system, ensuring proper upscaling without distortions between tiles. This entire process is illustrated in Figure 11, which shows the system used to upscale an image in C++ using the libtorch API.

The team computed variance with NumPy which helped to identify any potential issues that needed addressing and determine the appropriate variance threshold. Based on the variance calculation, the functional model sent the cropped image tile to either FSRCNN or interpolation for upscaling.

# 3.2 Model Training

Convolutional Neural Networks require trained weights for each convolutional stage, which are generated through machine learning. This machine learning implementation of super-resolution is a solved problem for modern datasets. If there is enough pixel density, creating pairs of images to train on is quite simple. On the other hand, upscaling retro video games presents a distinct challenge: style transfer. We chose a super-resolution model for upscaling that provides a low-operation, memory-efficient, and modular solution. We selected this as the top choice after examining [1], which demonstrated a successful real-time hardware upscaling system using FSRCNN. Developers typically create high-resolution and low-resolution image pairs for upscaling applications by downscaling the original image and then requiring the model to learn how to recreate it. The result usually produces an image of the same quality as the original, but with many times the number of pixels. Our application encountered several issues when implementing this approach. Additionally, modern image datasets have much higher quality than the raw Wii frames we worked with. The process of converting low-resolution frames back to their standard resolution counterparts did not yield the quality we had hoped for, which created a distinct challenge for our specific case.

This design utilizes a lightweight yet state-of-the-art model for image upscaling: FSRCNN. This model offers a balance between computational efficacy and the ability to enhance images suitable for an FPGA implementation. The team created low-resolution and high-resolution datasets from a Wii emulator before training the model. Various data augmentations, including random rotations, mirroring, and filters, are used to make the model as robust as possible on the available data.

Figure 11: A block diagram of the C++ system architecture.

# 3.2.1 Machine Learning Design Plan

The objective of the machine learning (ML) component of this project is to upscale native Wii frames by a factor of two, aiming to improve pixel density, texture clarity, and overall image quality. As a reference for visual fidelity, the team utilizes output from the Dolphin emulator, which provides a modern, high-resolution rendering of the game. This serves as a benchmark for evaluating the quality of upscaled frames.

The initial approach involves generating training data by downscaling high-resolution frames captured from the Dolphin emulator and training a super-resolution model to reconstruct the original resolution. This method is preferred over using upscaled images as ground truth because models trained on artificially upscaled data are constrained by the limitations of the underlying interpolation algorithm. In contrast, training on downscaled-original pairs allows the model to learn meaningful representations and recover lost detail during upscaling.

The original dataset consists of 3,266 full frames captured from the emulator at a resolution of  $1280 \times 720$  and a 16:9 aspect ratio. These frames are divided into  $64 \times 64$  pixel patches, which are then downscaled to  $32 \times 32$  to serve as low-resolution inputs. An FSRCNN model with 56 intermediate layers is trained on these  $32 \times 32/64 \times 64$  patch pairs to perform 2x image upscaling.

While initial results on emulator-derived data are promising, the model performs poorly when applied to frames captured directly from the Wii. The output exhibits limited improvement in pixel accuracy, texture clarity, and visual quality, indicating a mismatch between training data and real input conditions.

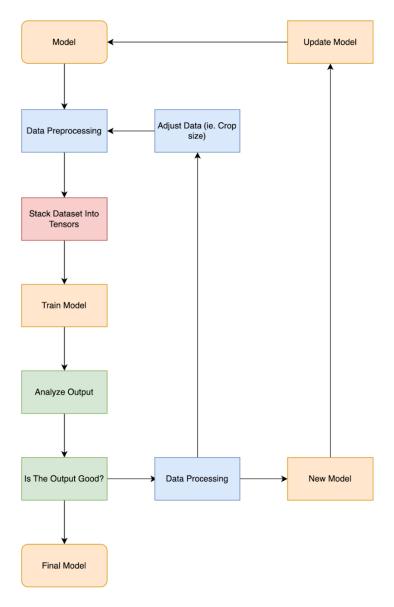

The team followed the design flow shown in Figure 12 throughout the model training process for

Figure 12: A flowchart detailing the process of determining next steps when training the model.

the initial FSRCNN for the emulated dataset.

#### 3.2.2 Training on an Emulated Dataset with Composite Video Artifacts

To address this discrepancy, the dataset is augmented by introducing composite video artifacts into the low-resolution patches, simulating the visual characteristics of native Wii output. However, retraining the model on this augmented dataset still does not yield a substantial improvement in performance on actual Wii frames.

In response, the team constructed a new dataset consisting of 1,893 full frames captured directly from the Wii at 576i resolution with a 4:3 aspect ratio. Using the same preprocessing methodology, these frames are divided into 64 x 64 pixel patches and downscaled to 32 x 32 to generate the low- and high-resolution training pairs. This new dataset provides training data that is better aligned with the visual characteristics of native Wii footage, forming the basis for subsequent model training and evaluation.

While this new model provides an overall better upscaled image, satisfying one of the three project goals (accurate pixel upscaling), two major challenges remain to be addressed being texture clarity and overall image quality.

### 3.2.3 Addressing Domain Shift

Texture clarity and sharpness prove to be a challenge without a straightforward solution. This problem, known as domain shifting, requires a specialized approach as it lacks a standard implementation method. A more resource-intensive model can be used to create a high-resolution dataset for Wii frames by which FSRCNN can be trained on. To address this issue, an implementation of a CycleGAN model [38] was used. CycleGAN attempts to translate an image from a source domain to a target domain.

After looking into CycleGAN, a more modern successor was found, called Contrastive Learning for Unpaired Image-to-Image Translation (CUT) [39]. This model uses the same generator and discriminator architecture, making CycleGAN a good baseline. As CUT outperforms CycleGAN on most metrics, the team decides to implement this approach.

The team trained the CUT model on uncurated  $256 \times 256$  pixel crops. Low-resolution Wii frames and high-resolution emulated frames are paired together so the model can learn how to transform Wii frames into the target domain of emulated frames. Due to the uncurated nature of the dataset, the results of CUT do not meet the team's quality standards.

#### 3.2.4 Current Implementation

The final model weights were trained from the Wii dataset using the FSRCNN model. The frames are cropped into  $64 \times 64$  pixel tiles, representing the high-resolution dataset. These tiles are then downscaled to  $32 \times 32$  pixel tiles, representing the low-resolution dataset. Then, a variance calculation was run on both datasets to remove tiles that did not provide much information, such as sky tiles, black tiles, or any tiles that were completely the same color, as they lacked texture. This addressed one of the three issues (pixel density). The final architecture of the FSRCNN implementation for the board constrained a  $7 \times 7$  kernel and 24 intermediate layers.

# 3.3 Managing Hardware Dataflow

The two major limitations on this project are time and resources. When testing the output video by simply passing it through the FPGA without any manipulation, the output FPS was 25. This number sets the target for what must be achieved for the design to qualify as a real-time system. Each frame, 414,720 pixels, has to be loaded into the system, split into 32 x 32 tiles, variance calculated, converted to RGB, upscaled using interpolation or FSRCNN, reassembled into the upscaled frame, and output to a frame buffer within 40 milliseconds before the next frame arrives. In addition to timing constraints, hardware limitations also narrow the capabilities of the entire system. When considering the resources of the ZCU102, the larger and more robust board the team worked with, it has a total of 1,824 BRAM blocks, 2,520 DSPs, 5,481,600 FFs, and 2,740,800 LUTs available to the user. Ensuring that every IP block created could fit within these constraints was one of the project's largest challenges.

The team first designed the architecture to target the KV260 development board, an entry-level evaluation platform for the Zynq Ultrascale+ series SoCs, as it was an affordable and seemingly suitable option at the project's inception. Later, the team received a more capable ZCU102 development board and ported all the progress we had made up to that point onto it. All IP was to interface with each other via AXI-Stream, a high-bandwidth interconnect system designed by ARM, and operate on 28 x 28 pixel tiles [40]. Later, the team switched to 32 x 32 pixels to avoid dealing with partial stream transfers. To maximize bandwidth and minimize the data-streaming bottleneck, all IP blocks were developed to be data-driven and have a top-level interface stream width of 128 bits.

Since each IP block expected data to arrive as 32 x 32 tiles in a raster format, but image frames are stored in DRAM linearly, the design required a way to reformat the data. One option was to store the image frame in on-chip Block RAM (BRAM), one block per row of pixels, and to simply read 32 pixels from the first RAM, 32 from the second, and so on, until a full tile was read, but this exceeded the resources available on the KV260. The second option, and the one the team used, was to instead send tiles down one row at a time using an AXI-DMA core in scatter-gather mode to fetch the relevant sections of an image. This, however, created a bottleneck. With a 128-bit stream interface, two bytes per YUV 4:2:2 pixel, and 32 pixels per row in a tile, only four stream beats of data could be output before the DMA engine needed to start a new transfer. This ended up adding a significant amount of latency to the design, since the DMA engine would need to access DRAM to fetch a new buffer descriptor every four stream beats. A single DRAM chip was shared with PetaLinux, indicating a busy memory interface.

The format of the AXI-Stream interface between IP blocks in the tile pipeline is the following: {0BGR-0BGR-0BGR-0BGR}. If the RGB values were sent out without padding, each AXI-Stream transfer would contain 5.333 pixels, making storage and indexing of pixels down the pipeline much more difficult. The team opted to simplify code and calculations at the expense of slightly more memory. This could be further optimized in the future, making every AXI-Stream contain only valid pixel data and no padding. However, handling the pixels would be much more difficult and wouldn't be worth the effort for the timeline of this project.

One additional piece of hardware at the end of the pipeline is a block that converts RGB 8:8:8 to RGB 5:6:5. Most of the system operates in the RGB 8:8:8 color space to preserve a higher level of detail, but the frame buffer of the PetaLinux installation on the KV260 and ZCU102 expects data in RGB 5:6:5 format. A simple IP in Verilog clips the least significant bits from each color channel and repacks the data. For each pixel, R and B are clipped to remove the 3 least significant bits, and G has its 2 least significant bits removed. This results in a final AXI-Stream width of 64 bits sent into the SG-DMA, since half of the bits from the 32-bit RGB 8:8:8 are removed.

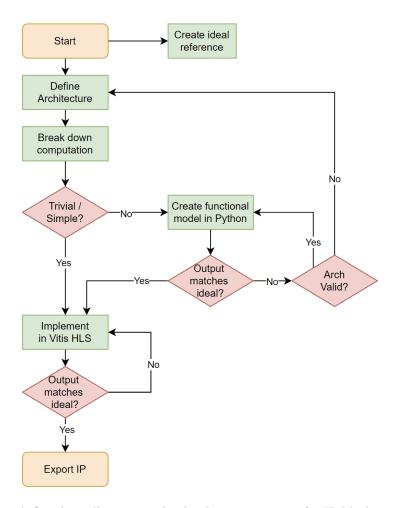

# 3.4 High-Level Synthesis Development

A consistent design methodology is employed across all blocks developed in HLS, as illustrated in the flowchart (Figure 13). To begin, the team created an example stimulus for each block to use. This could be used by self-tests and verification implementations to confirm the accuracy of the intended result. While it isn't a replacement for extensive testing, it is foundational to the initial development of upscaling blocks since it illustrates the visual result of a successfully upscaled tile and provides known values to reference when manually debugging.

While the ideal reference is created, each IP's architecture is defined. This results in high-level block diagrams that illustrate the general inputs, outputs, and internal features of each block. Not only is this essential for creating a development framework, but it also provides an understanding of how data should be transferred to and from a block, allowing verification tests to accurately build these connections.

After the general architecture was defined, the computations required were analyzed. If the expected necessary calculations for a given block are deemed trivial, implementation would start immediately in HLS; however, if the block is complex, a functional model would first be created in Python. This functional model enables the team to test whether the architecture produces the expected output, and if not, to highlight the need to debug the Python model or reevaluate the validity of the proposed architecture. If the functional model correctly calculates the expected input, implementation could begin in HLS using the structure of the functional model as a framework. Creating functional models in Python can save a lot of time in the design process, as it eliminates high-level bugs in an architecture before starting the longer process of implementing a design in HLS.

Once a block is created in HLS, it is verified against an extensive testbench to confirm that its implementation matches the expected outcome. These testbenches also enable the cosimulation of the block, providing waveforms of the IP's input and output signals. These signals are essential for confirming that the block interfaces correctly with the overall system and can be used to calculate the block's process time.